著录项信息

| 专利名称 | 基于FPGA的数字OSD控制器 |

| 申请号 | CN200510041056.2 | 申请日期 | 2005-07-15 |

| 法律状态 | 权利终止 | 申报国家 | 中国 |

| 公开/公告日 | 2005-12-28 | 公开/公告号 | CN1713264 |

| 优先权 | 暂无 | 优先权号 | 暂无 |

| 主分类号 | 暂无 | IPC分类号 | 暂无查看分类表>

|

| 申请人 | 合肥工业大学 | 申请人地址 | 安徽省合肥市屯溪路1***

变更

专利地址、主体等相关变化,请及时变更,防止失效 |

| 权利人 | 合肥工业大学 | 当前权利人 | 合肥工业大学 |

| 发明人 | 盛磊;徐科军 |

| 代理机构 | 安徽省合肥新安专利代理有限责任公司 | 代理人 | 何梅生 |

摘要

基于FPGA的数字OSD控制器,其特征是在FPGA上实现,由基于字符的处理模块、基于可变位图的处理模块、微控制器MCU接口模块、OSD图像色彩与特性合成模块和OSD管理模块组成;利用所设计的三种不同作用和不同类型存储器,自动合成符合不同分辨率LCD扫描时序、彩色数字OSD图像信号流,与原始输入图像在输出端进行图像叠加,在LCD上显示出图像色彩、显示位置、图像窗口大小、字符大小、透明度都可变的OSD菜单图像。并为用户所使用的MCU提供串并行接口,方便用户的硬件设计和软件编程。

1.一种基于FPGA的数字OSD控制器,其特征是在FPGA上实现,并由基于字符的 处理模块、基于可变位图的处理模块、微控制器接口模块、OSD图像色彩与特性合成模块 和OSD管理模块组成;所述基于字符的处理模块中的OSD窗口RAM采用FPGA中的分 布式存储器资源,并设置为双端口RAM的形式,其数据是由用户微控制器写入,包括字 符编码和属性字段;所述基于字符的处理模块中的OSD字体ROM采用FPGA中的块存 储器资源,并设置为只读存储器的形式,其每个像素点设置为n位,利用对应的彩色查找 表,获得在每个字符区域中的2n种颜色的显示;所述基于字符的处理模块的OSD图像合 成采用从OSD窗口RAM到OSD字体ROM之间的访问地址转换逻辑,使用4个计数器与 比较器完成地址转换;所述基于可变位图的处理模块中的位图RAM是采用FPGA内的块 存储器资源,设置为双端口RAM的形式,位图RAM的位宽、地址深度、行像素点数的 数值,可以根据要求OSD图像的颜色位数和不同分辨率图像来任意设置;所述OSD图像 色彩与特性合成模块根据OSD控制器的控制参数和显示窗口的属性参数,生成包含字符 和位图的OSD图像数据编码流;利用OSD图像数据编码流及当前显示像素点的属性参数, 合成最终的数字红绿蓝3*8bits的彩色OSD图像数据流,同时OSD管理模块输出OSD图 像数据流有效信号,用于指示当前OSD图像数据有效,将当前有效OSD图像数据与原始 输入视频图像数据进行叠加;

通过由所述MCU接口模块提供的串并两种方式之一,设置OSD控制器内的控制寄存 器和属性参数寄存器、读取OSD控制器的当前工作状态、设定OSD窗口存储器和位图存 储器的显示信息;

利用FPGA片内存储器资源,实现数字OSD图像的生成;OSD图像中不同区域的字 符、位图之间的链接关系由OSD控制器的数字逻辑负责计算与处理。

2.根据权利要求1所述的控制器,其特征是所述数字OSD控制器与用户微控制器的 接口包括并行的扩展存储器接口和串行外设接口。

3.根据权利要求1所述的控制器,其特征是所述数字OSD控制器与LCD显示控制 板中的LCD的各图像处理模块进行连接,接受其输出的行同步信号、垂直同步信号以及 使能信号,并在原始输入图像数据流中插入由所述控制器生产的OSD图像数据流,将叠 加了OSD图像的数据流送入LCD显示面板。

技术领域:

本发明涉及一种OSD(On Screen Display,屏幕显示)控制器,特别是一种为液晶显示器 LCD提供数字OSD图像、用现场可编程门阵列FPGA实现的OSD控制器。

背景技术:

OSD是各种显示器都必须具备的一项功能,为用户提供对显示器进行参数调节的字符 或图像信息,方便用户对显示器进行调节。此外,还可以在原始视频图像上叠加特殊的图 像信息。OSD控制器就是完成这项功能的系统。

田日镇设计的屏幕显示电路用于显示模拟的隔行扫描视频信号的显示系统中(“视频 显示设备的屏幕显示电路”,中国专利,公告号1139334,1997.1.1)。但它不能用于LCD, 因为LCD接收的是数字逐行扫描的视频信号,显示数据必须与LCD的物理像素点一一对 应,需要一种数字信号的OSD显示菜单生成方法。

J.A.库佩尔和J.W.查纳提出了一种OSD控制器的结构(“屏幕显示的链接目录结 构”,中国专利,公告号1197570,1998)。它包括一组OSD存储器存储块序列,每块包含 表示OSD的数据和指向下一块的指针。这些块由OSD发生器按顺序地从OSD存储器中 检索,并且从OSD表示数据中生成OSD图像表示信号。由于它在OSD显示菜单的不同 区域中,所以采用链表目录结构,这样在用户编程时就需要计算和指定下一块的指针。又 因为是直接从OSD存储器中检索出OSD数据,就相当于OSD图像的每个像素点的数据 都要由微控制器(MCU)写入OSD存储器中,所以增加了编程的工作量和复杂性。此外, 存储器的使用量也较大。

汤姆森消费电子有限公司研究采用1-位像素产生屏幕显示消息的设备和方法(“采用 1-位像素产生屏幕显示消息的设备和方法”,中国专利,公告号:CN1239628A,1999.12.22), 其OSD位流包括OSD首标和OSD数据。这些首标和数据完全是由MCU写入存储器,虽 然它使用了1-位像素的有效OSD位流,降低了对译码/显示系统的存储器带宽要求,但是, 由于每一个OSD显示像素点的都要在存储器中建立,所以,存储器容量至少要与OSD图 像的总分辨率保持一致。另外,首标还要占用存储器空间。例如,该专利给出的一个实施 例中,每个首标是由5个64位字构成,其后是任意数量的64位OSD数据(位表)字。 可见,它只是相对于“多位”OSD位流的方法降低了存储器容量,实际的存储器总容量仍 然很大。

日本的MasayukiNaito和Sano-shi提出一种在移动电话上显示电视图像时,叠加OSD 图像信息的相关技术(“Image signal processor circuit and portable terminal device”,美国专 利,公告号:US2005/0057582,May 17,2005)。该专利只采用OSD处理单元内的字符(图) 库(FROM)来产生OSD图像,不能够产生随意变化的OSD图像。

发明内容:

本发明是为避免上述现有技术所存在的不足之处,提供一种以FPGA为核心的,仅使 用FPGA片内少量存储器资源,具有显示字符和位图两种功能,用户的硬件接口和软件编 程简单的基于FPGA的数字OSD控制器。

本发明解决技术问题采用的技术方案是:

本发明结构特点是在FPGA上实现,并由基于字符的处理模块、基于可变位图的处理 模块、MCU接口模块、OSD图像色彩与特性合成模块和OSD管理模块组成;

通过由所述MCU接口模块提供的串并两种方式之一,设置OSD控制器内的控制寄存 器和属性参数寄存器、读取OSD控制器的当前工作状态、设定OSD窗口存储器和位图存 储器的显示信息;

所述OSD图像色彩与特性合成模块根据OSD控制器的控制参数和显示窗口的属性参 数,生成包含字符和位图的OSD图像数据编码流(OSD_DCODE);利用OSD图像数据编 码流(OSD_DCODE)及当前显示像素点的属性参数,合成最终的数字红绿蓝(RGB)3*8bits 的彩色OSD图像数据流,同时OSD管理模块输出OSD图像数据流有效信号 (OSD_ACTIVE),用于指示当前OSD图像数据有效,将当前有效OSD图像数据与原始 输入视频图像数据进行叠加;

利用FPGA片内存储器资源,实现数字OSD图像的生成;OSD图像中不同区域的字 符、位图之间的链接关系由OSD控制器的数字逻辑负责计算与处理。

本发明的结构特点也在于:

所述利用FPGA片内存储器资源是分别采用分布式存储器资源(Distributed RAM)和 块存储器资源(Block RAM)。

在于所述字符处理模块的OSD窗口RAM(OSD_WRAM)采用FPGA中的分布式存 储器资源(Distributed RAM),并设置为双端口RAM的形式;OSD字体ROM(OSD_TROM) 采用FPGA中的块存储器资源(Block RAM),并设置为只读存储器的形式。

所述字符处理模块的OSD图像合成采用从OSD窗口RAM(OSD_WRAM)到OSD字 体ROM(OSD_TROM)之间的访问地址转换逻辑,使用4个计数器与比较器完成地址转换。

所述OSD窗口RAM(OSD_WRAM)中的数据是由用户微控制器(MCU)写入,包 括字符编码和属性字段。

所述OSD字体ROM(OSD_TROM)中的每个像素点设置为n位,利用对应的彩色查找 表,获得在每个字符区域中的2n种颜色的显示。

基于可变位图处理模块的位图RAM(BMP_RAM)是采用FPGA内的块存储器资源 (Block RAM),设置为双端口RAM的形式,位图RAM(BMP_RAM)的位宽、地址深 度、行像素点数(OSD_PX)的数值,根据要求OSD图像的颜色位数和不同分辨率图像任 意设置。

所述数字OSD控制器与用户微控制器的接口包括并行的扩展存储器接口和串行外设 接口(SPI)。

所述数字OSD控制器与LCD显示控制板中的LCD的各图像处理模块进行连接,接 受其输出的行同步信号(Hsync)、垂直同步信号(Vsynnc)以及使能信号(Enab),并在 输入原始图像数据流中插入由所述控制器生产的OSD图像数据流,将叠加了OSD图像的 数据流送入LCD显示面板。

用户通过MCU接口模块提供的串并两种方式之一,设置控制器内的控制寄存器、属 性参数寄存器,读取控制核的当前工作状态,设定OSD窗口存储器(OSD_WRAM)和位 图存储器(BMP_RAM)的显示信息;利用OSD窗口存储器(OSD_WRAM)、OSD字体 ROM(OSD_TROM)、位图存储器(BMP_RAM)三种不同作用和不同类型的存储器资源中 存储的数据信息,生成符合不同分辨率LCD面板的工作时序要求的彩色OSD图像;OSD 图像色彩与特性合成模块将根据控制器的控制参数和显示窗口的属性参数,包括在LCD 上显示出的字符编码、字符颜色、位图像素点数据、位图像素点颜色、OSD图像的显示位 置、OSD图像窗口大小、显示字符大小、以及OSD图像的透明度,生成包含字符和位图 的OSD图像数据编码流(OSD_DCODE);利用OSD_DCODE及当前显示像素点的属性参 数,合成最终的数字红绿蓝(RGB)3*8bits的彩色OSD图像数据流,同时OSD管理模块 输出OSD图像数据有效信号(OSD_ACTIVE),用于指示当前OSD图像数据有效,并使 当前有效的OSD图像数据与输入的原始视频图像数据进行合成。

与已有技术相比,本发明的有益效果体现在:

1、本发明仅使用FPGA片内少量的存储器资源,实现数字OSD图像的生成,没有使 用独立的、大容量的、片外存储器资源,从而优化控制器的结构,降低成本;

2、本发明中包括基于字符和基于可变位图的两种OSD图像合成模块,可以表达丰富 的信息,优于仅采用一种合成模块的OSD控制器,OSD图像显示与调整更为灵活;

3、本发明OSD图像中不同区域的字符、位图之间的链接关系完全由OSD控制器的 数字逻辑负责计算与处理,不需要用户在软件编程时考虑,从而降低用户编程的复杂度, 方便用户的使用,优于在MCU编程时需要考虑OSD图像之间的链接关系的合成方法;

4、本发明OSD控制器具有串行、并行两种MCU接口,为用户的硬件设计和软件编 程提供了较大的自由度,使其适用于采用不同类型MCU的LCD控制器中,优于只采用单 一MCU接口的控制器;

5、在实际性能方面,本发明在XILINX公司的SPARTAN2E系列FPGA中的一个实 施例中,工作频率最高达到85MHz,并通过高低温度的试验,证明能够可靠工作在-40℃~ +85℃的温度范围内,优于一般OSD控制器只能工作于0℃以上的环境温度中。

附图说明:

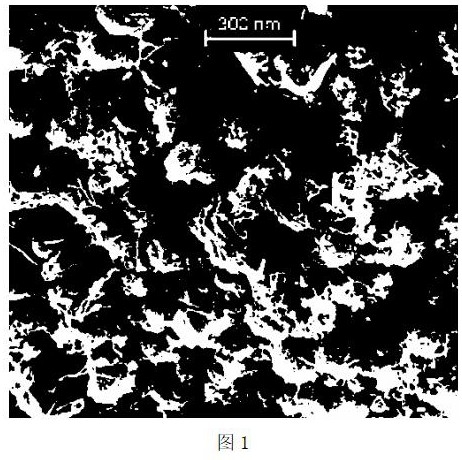

图1为OSD控制器内部功能模块框图。

图2为字符处理模块的存储器配置原理图。其中:

图2a为OSD_WRAM组织结构示意图。

图2b为字符(CELL)组织结构示意图。

图2c为OSD_TROM组织结构示意图。

图3为位图处理模块的存储器配置原理图。

图4为OSD字符图像合成原理图。

图5为OSD位图图像合成原理图。

图6为该OSD控制器与LCD显示系统中其它部分的连接关系图。

图7为并行扩展存储器接口和串行SPI接口设计原理。

具体实施方式:

下面结合附图和实施例对本发明作详细说明。

参见图1,本实施例中,基于FPGA的数字OSD控制器的设计目标是生成用户自定义 的OSD数字图像,并使之能够与数字化的、高速的原始视频图像数据流进行叠加,形成 新的数字图像,然而,由于视频图像不停地在刷新,OSD图像要在时序扫描到它所在区域 和对应像素点时,准备好像素点的RGB值,而这些数据是以存储器形式来组织的。注意, 那里并不是简单地以图像的方式存储在存储器中。

图2所示基于字符和图3所示基于位图的两个OSD图像合成模块分别采用了不同的 存储器配置方案。

图2为字符处理模块的存储器配置原理的一个实现例,本实施例为其配置了两个存储 器:一个称为OSD窗口RAM(OSD_WRAM),一个称为OSD字体ROM(OSD_TROM), 它们都嵌入在FPGA中,分别占FPGA的Distribute RAM和Block RAM逻辑资源。具体 的存储器组织结构如图2所示,图2a中OSD_WRAM是用户可以通过MCU串并两种接口 来设置的双端口静态SRAM,共有256个地址单元,每个地址单元是16bits,用于存储显 示字符编码及字符属性。OSD窗口被划分为若干行列,构成一个矩形的显示窗口,OSD 窗口水平和垂直方向的宽、高和显示位置(起始点X,Y坐标)由4个参数寄存器(OSD_WX、 OSD_WY,和OSD_XSTART、OSD_YSTART)进行控制,终止点坐标(OSD_XSTOP, OSD_YSTOP)由内部逻辑计算得到,并且进行超出边界检测,防止因单片机编程误操作 出现图像紊乱。图中的一个实例为4行*8列。而每个字符单元被称为CELL,由n*m像素 分辨率的点阵组成,如图2b所示一个实施例中CELL的分辨率为24*16pixels,每个像素 点占1bit的RAM位。为方便存取,将一行共16个像素点组成一个存储单元,那么一个 CELL就是由24个16bits的存储单元构成,占用24个ROM地址,把所有的预置字符顺序 地存储在OSD_TROM中,便有如图2c所示的字符库结构。注意,对于本领域的技术人员, 存储器OSD_WRAM和OSD_TROM的位宽、地址深度、字符CELL的宽高比和像素点数 目等数值,都不仅限于图2实例中的设计值,因此采用此种配置方案可以实现多种基于字 符的OSD图像。

图2中的字库OSDT_ROM中存储的字符信息,一部分是固定的字符,另一部分是由 MCU写的新字符库,这样可以显示丰富的用户自定义字符。

图3为位图处理模块的存储器配置原理的一个实例。在该实例中,包含一个双端口的 位图RAM(BMP_RAM),组织结构如图3所示。在垂直方向上,它对应着4行图像扫描 的像素点数据;根据LCD面板的水平分辨率,OSD_PX配置为不同的长度,但为了方便 设计,OSD_PX与字符的宽度(16位)保持一定的比例关系,必须是16的整数倍,最大 为1024,这样BMP_RAM总共只占用FPGA的一个Block RAM(4Kbits)资源。如果把 每1位扩展为4位,可以实现16种不同的彩色图形。整个OSD图像在垂直方向上,每4 行被划分为一个独立的区域,在显示时序扫描到OSD图像显示区域内某一行前,用户需 要通过MCU接口提前更新BMP_RAM的内容。以这种方式合成的OSD图像,可以实现 用户自定义位图,比较基于字符方式中的通过用户定义字符库来增加显示信息方法,可以 实现更丰富的自定义图像图形信息。注意,对于本领域的技术人员,存储器BMP_RAM的 位宽、地址深度、OSD_PX的数值等,都不仅限于图3实例中的设计值,因此采用此种配 置方案可以实现多种基于位图的OSD图像。

图4为OSD字符图像合成原理图。在本实施例中,确定OSD控制核的存储器组织结 构(图2和图3)后,利用这些存储器资源,就可以合成所需要的OSD图像。合成OSD 图像是由OSD窗口扫描检测逻辑来实现,包括一系列的OSD图像合成逻辑控制功能。其 中,从OSDW_RAM中显示字符编码的存储地址(逻辑地址),得到最后在LCD屏上显示 的某个OSD像素点在OSDT_ROM中实际对应的物理地址,这之间的地址转换逻辑是OSD 图像合成的关键。

在图4的实例中,除了包括2个存储器OSDW_RAM和OSDT_ROM外,主要有2个 扫描时序计算逻辑单元、4个比较器和字库ROM访问地址计算单元。以像素为单位的CELL 内扫描时序计算单元是在一个字符内部,按像素点时钟频率DCLK(例如在一个实例中, 对应于1024*768*60Hz的逐行扫描PC视频信号,DCLK为65MHz)计算出即将显示像素 点所对应的坐标;以字符为单位的OSD窗口内扫描时序计算单元是按DCLK/FR_X的分频 时钟计算出即将显示哪个字符;而它们分别被两个比较器1,2,3,4的输出信号控制,最终得 到访问双端口OSDW_RAMB端口的读地址(OSDW_AD,它是逻辑地址)和读信号(RD)、 使能信号(OE),从而由OSDW_RAM的B端口输出OSD显示图像中对应坐标区域的字 符编码数据(OSDW_DATA)。

字符编码数据(OSDW_DATA)是用户通过MCU接口写入OSDW_RAM的16位字符 编码信息,在它的一个实例中,其定义如图5所示,包括字符编码和字符属性,具体的包 含三个字段:(1)字符索引码char_code,8bits,一共可以编码检索预先存放在OSDT_ROM 字库中的256个固定字符,包括英文字母大小写、数字、固定图标、和常用汉字;(2)前景 色frontcolor,4bits,定义16种颜色;(3)背景色backcolor,4bits,对应16种颜色。采用 这个色彩属性就可以实现“热点”图标,指示当前的工作点。

字库OSDT_ROM的访问地址计算单元利用OSDW_DATA的字符索引码字段char_code 和字符内扫描参数celly_cnto,按下面的公式,先计算出当前显示图像像素点在OSDT_ROM 的页地址,再加上celly_cnto得到物理地址OSDT_AD,同时按照时序关系给出对应的OSD 图像数据有效信号OSD_ACTIVE信号。图4中的时钟延迟单元是补偿计算和存储器访问 过程中的流水线延迟,使最终输出的OSD图像数据码流(OSD_DATA)与OSD_ACTIVE 同步。

OSDT_AD=charcode*FR_X+celly_cnto

OSD图像数据码流(OSD_DATA)和对应字符编码定义中的两个字段(背景色和前景 色)一起进入图1的“OSD图像色彩与特性合成模块”,由其中的彩色查找表(CLUT), 合成最终输出到LCD的数字RGB 3*8bits的视频图像数据流。此外,通过把OSD图像数 据与原图像进行bit连接(&),实现“透明OSD”图像的显示效果。根据时序控制寄存器 的设置,调整OSD控制核的时钟频率在水平扫描方向为原频率的二分频,并在垂直扫描 方向上,采用数据复重的方法,实现OSD显示图像的二倍放大。

OSD图像是LCD显示器的必备功能,根据本发明设计的一个实施例,如图6所示, OSD控制器作为LCD控制器的一个功能模块,集成于FPGA内。由LCD控制器的其它图 像处理模块输出一路3*8位的数字RGB图像信号到OSD控制器。当微控制器写入控制字, 将OSD使能信号(OSD_EN)置为有效“1”时,OSD控制器产生的OSD图像信号(3*8 位RGB)与输入的数字RGB图像信号叠加在一起。叠加是在水平、垂直同步信号扫描到 OSD图像所在区域时,利用OSD图像有效信号(OSD_ACTIVE)的高低电平,选通OSD 图像数据输出到LCD,取代输入图像数据,实现OSD图像的显示。根据本发明,OSD图 像数据可以部分取代输入图像数据,从而实现透明度可调的OSD图像。

OSD控制器中集成两种存储器接口:并行的异步扩展存储器和串行的SPI接口,图6 中MCU可以通过这两种接口设置OSD控制器的工作状态进行控制,负责启动OSD控制 器工作,设定OSD图像中字符信息和位图信息,设定OSD图像显示位置的坐标值及OSD 显示窗口的大小、字符和位图的大小、透明程序等属性。

在图6中,OSD控制器的用户通过MCU接口模块提供的串并两种接口方式之一,来 设置OSD控制器内的控制寄存器、时序参数寄存器、OSD显示窗口属性寄存器、图像属 性参数,读取当前工作状态和OSD显示窗口的数据,设定OSD窗口存储器(OSD_WRAM) 和位图存储器(BMP_RAM)的显示信息;OSD图像色彩与特性合成模块则根据上述各种 控制参数、OSD显示窗口属性参数,生成包含有字符和位图两种信息的OSD图像数据编 码流(OSD_DCODE);利用OSD_DCODE及当前显示像素点的图像属性参数,通过两张 彩色查找表生成共24位(3*8)的数字红(R)、绿(G)、蓝(B)信号,形成最终的彩色 OSD图像数据流,同时由时序处理管理模块输出一个用于指示当前OSD图像数据有效的 OSD_ACTIVE信号,以便与原始输入图像数据进行叠加。

注意,当字库OSDT_ROM中字符和位图BMP_RAM的每一个像素点的位数取为1时, 通过彩色查找表,可以译码得到21种颜色;当每一个像素点的位数取为2时,通过彩色查 找表,可以译码得到22=4种颜色;以此类推,当每一个像素点的位数取为n时,通过彩 色查找表,可以译码得到2n种颜色,最大的位数n可以取到8位,译码得到256种颜色, 从而实现在一个字符区域和位图区域内显示多种颜色的字符和位图。

为提高OSD控制核与用户MCU的兼容性,并方便用户MCU的硬件接口和软件程序 设计,MCU接口模块提供并行、串行两种接口逻辑控制单元:

(1)与MSC51系列单片机的P0、P2口,按照其外围扩展存储器的数据和地址总线接口 方式来通讯。P0口复用为8位数据总线和低8位地址总线,P2口为高8位地址总线。MCU 接口逻辑模块进行地址译码,8位数据到16位寄存器或16位RAM的转换。MCU通过一 条MOVX指令可以直接访问控制核内8位寄存器,两条MOVX指令(可以不连续)对相 邻的两个地址即可完成对一个16位寄存器的访问,两条连续的MOVX指令对两个相邻的 地址进行操作即可完成对一个16位RAM单元的访问。

(2)采用四线的SPI串行通讯接口协议,与包括MSP430和MCS51等类型单片机进行串 行通讯。SPI接口逻辑单元内部串行通讯协议是由一个状态机(State Machine)来实现,状 态转移图如图7所示。SPI接口逻辑的输入端口包括四根信号线:SCK(串口时钟),CE (使能信号),DI(数据输入),DO(数据输出)。包括6个状态:IDEL(空闲状态),START (开始),ADDRESS(输入地址状态),RW(读写判断位),READ(读状态),WRITE(写 状态)。在接收到访问地址后的下一位是读写命令判断位,决定接下来是读数据,还是写 数据。完成读写命令,必须再进入一次IDEL状态一个时钟周期后,才能重新进入START 状态。

法律信息

- 2011-09-21

未缴年费专利权终止

IPC(主分类): G09G 3/36

专利号: ZL 200510041056.2

申请日: 2005.07.15

授权公告日: 2008.01.16

- 2008-01-16

- 2006-02-22

- 2005-12-28

引用专利(该专利引用了哪些专利)

序号 | 公开(公告)号 | 公开(公告)日 | 申请日 | 专利名称 | 申请人 |

1

| | 暂无 |

2003-10-06

| | |

2

| | 暂无 |

1999-04-28

| | |

3

| |

1998-09-23

|

1998-03-17

| | |

4

| |

1997-06-25

|

1995-05-30

| | |

5

| | 暂无 |

1999-06-30

| | |

被引用专利(该专利被哪些专利引用)

序号 | 公开(公告)号 | 公开(公告)日 | 申请日 | 专利名称 | 申请人 | 该专利没有被任何外部专利所引用! |